|

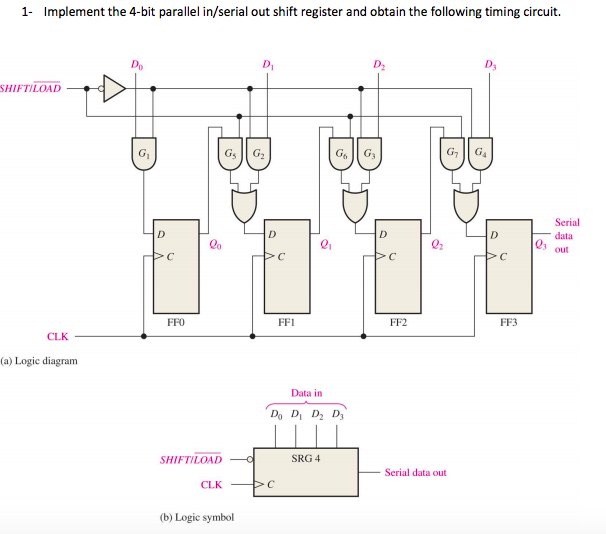

At each clock cycle, the content of the register shifts to the right and.

8 Bit Parallel In Serial Out Shift Register Vhdl Code Code In APut the code in a clocked process and tap the last bit in the vector, and you have your shift register.Please try again.

Epost GIVE ME In-depth 8 ways to create a shift register in VHDL Wednesday, Dec 11th, 2019 There are many ways to create a shift register in VHDL, though not all of them are equal. You can dramatically reduce the number of consumed resources by choosing the right shift register implementation for your needs and FPGA architecture. Every time a new element enters the queue, it shifts the existing ones one place further away from the input.

This article will only consider the shift register, even though there exist data structures that use fewer resources for larger FIFOs. 8 Bit Parallel In Serial Out Shift Register Vhdl Code How To Create ARead about how to create a ring buffer FIFO in block RAM to learn about such a solution thats not a shift register. While any shift register is suitable for creating generic, smaller buffers, there are methods of efficiently creating larger ones. Many FPGAs have logic elements that can double as specialized shift register primitives. You can improve performance in magnitudes by being mindful of how you write your VHDL code. The 1-bit shift register with generic depth Lets first have a look at different methods of creating a one-bit shift register. The input and output of this shift register is a single bit, a stdlogic value. We will use the entity declaration shown below for all of the following examples involving one-bit shift registers. To keep it simple, were going to use the same entity for multiple architectures, even though the rst and enable inputs are unused by some of them. These are the resources consumed for Xilinx, Intel (Altera), and Lattice FPGAs with the srdepth generic set to 128. Xilinx Vivado (Zynq): 4 LUTs (LUTRAM) 2 FFs Intel Quartus II (Cyclone V): 11 ALMs 1 BRAM Lattice IceCube2 (iCE40): 128 FFs Even though the shift register should require 128 flip-flops (FFs), we see that the resource usage reported by Vivado and Quartus is far less. Instead of using expensive FFs, the synthesis tools have used special built-in features of the logic blocks. Lookup tables (LUTs) used in such a way are counted as LUTRAM in the Vivado resource usage report. In the Intel FPGA, adaptive logic modules (ALMs) and one block RAM (BRAM) is used instead of flip-flops. Intel uses a technology that they call ALTSHIFTTAPS for implementing RAM-based shift registers. The Lattice iCE40 FPGA, which I used in this example, doesnt have an alternative option for packing 1-bit shift register, so its implemented entirely in 128 FFs. However, we shall see later in this article that the Lattice device can pack wider shift registers into block RAM. Need the ModelSim project files Let me send you a Zip with everything you need to get started in 30 seconds How does it work Tested on Windows and Linux Loading Gif. Give me the files Unsubscribe at any time Slicing the vector The most straightforward way to create a shift register is to use vector slicing. Insert the new element at one end of the vector, while simultaneously shifting all of the others one place closer to the output side.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed